La Taiwan Semiconductor Manufacturing Co. (TSMC) vient de dévoiler officiellement son nœud de 2 nm, baptisé N2. Prévu pour 2025, ce nouveau procédé introduira une nouvelle technologie de fabrication. Selon le teaser de TSMC, le processus 2 nm offrira soit une augmentation des performances pures par rapport à son prédécesseur, soit, lorsqu’il sera utilisé aux mêmes niveaux de puissance, il sera beaucoup plus économe en énergie.

TSMC a longuement parlé de la nouvelle technologie 2N, expliquant les rouages de son architecture. Le 2N sera le premier nœud de TSMC à utiliser des transistors à effet de champ à grille périphérique (GAAFET) et multipliera par 1,1 la densité des puces par rapport au nœud N3E. Avant même la sortie du 2N, TSMC lancera des puces en 3 nm, qui ont également été annoncées lors du symposium technologique TSMC 2022.

Le nœud de 3 nm sera décliné en 5 niveaux différents et, à chaque nouvelle version, le nombre de transistors augmentera, ce qui permettra d’accroître les performances et l’efficacité de la puce. En commençant par le N3, TSMC lancera ensuite le N3E (Enhanced), le N3P (Performance Enhanced), le N3S (Density Enhanced), et enfin, le N3X « Ultra-High Performance ». Les premières puces de 3 nm devraient être lancées au cours du second semestre de cette année.

Si le processus 3 nm est plus proche de nous en termes de date de lancement, c’est le 2 nm qui est légèrement plus intéressant, même s’il faut encore attendre quelques années. L’objectif de TSMC avec le nœud 2 nm semble être clair : augmenter la performance par watt pour permettre des niveaux de rendement et d’efficacité plus élevés. L’architecture dans son ensemble a beaucoup à offrir. Prenons l’exemple des transistors GAA nanosheet. Ils possèdent des canaux entourés de grilles de tous les côtés. Cela réduit les fuites, mais les canaux peuvent également être élargis, ce qui améliore les performances. Par ailleurs, les canaux peuvent être rétrécis pour optimiser le coût énergétique.

Le N3 et le N2 offriront tous deux des augmentations de performance considérables par rapport au N5 actuel, et tous offrent le choix d’équilibrer la consommation d’énergie avec la performance par watt. À titre d’exemple (d’abord partagé par Tom’s Hardware), en comparant le N3 au N5, on obtient un gain de 15 % en performances brutes et une réduction de la consommation d’énergie de 30 % lorsqu’il est utilisé à la même fréquence. Le N3E portera ces chiffres encore plus loin, respectivement jusqu’à 18 % et 34 %.

TSMC ne commencera pas la production de masse avant 2025

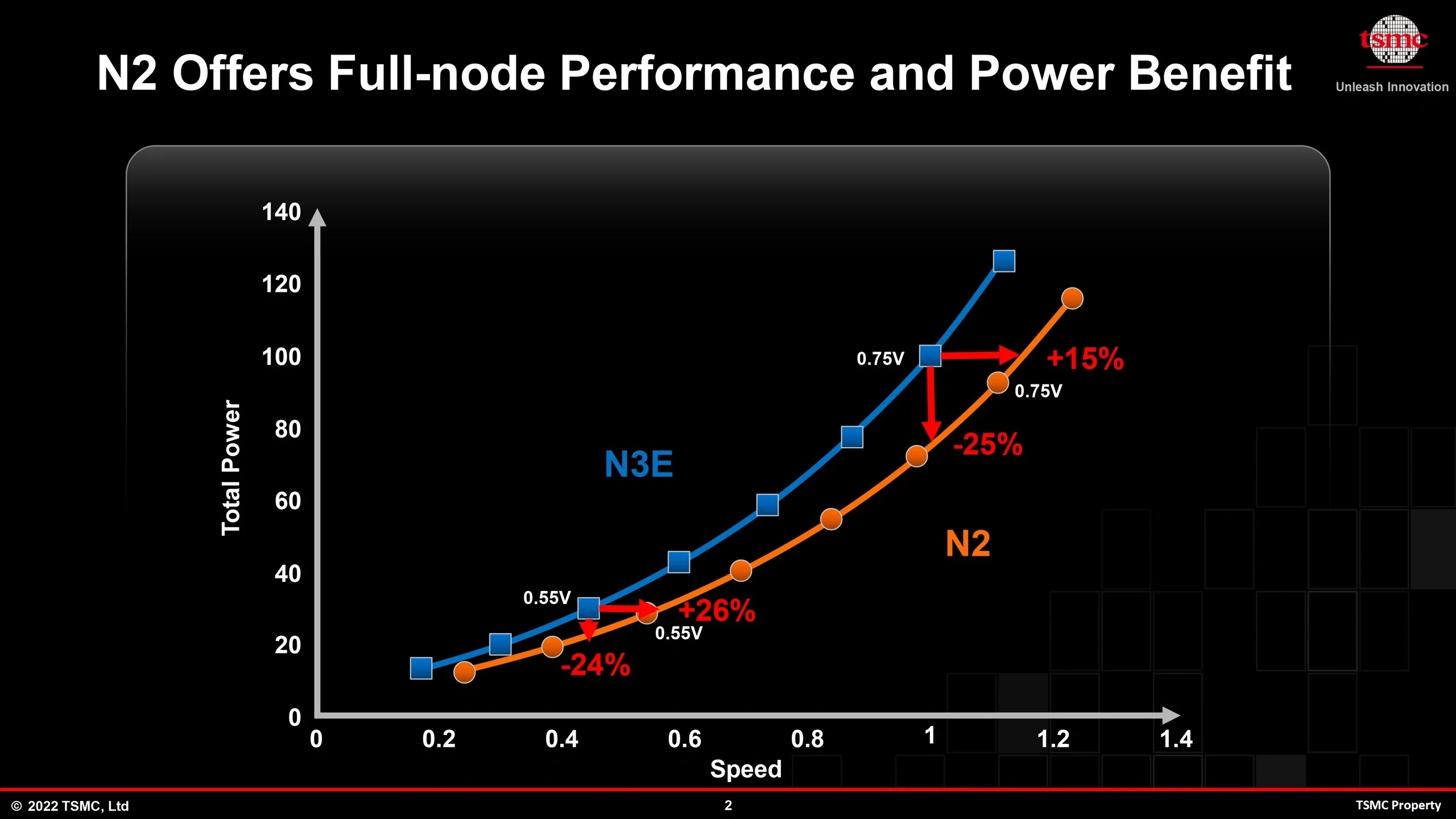

C’est avec le N2 que les choses commencent à devenir intéressantes. Nous pouvons nous attendre à une augmentation des performances allant jusqu’à 15 % lorsqu’il est utilisé avec la même consommation d’énergie que le nœud N3E, et si la fréquence est ramenée aux niveaux fournis par le N3E, le N2 offrira une consommation d’énergie jusqu’à 30 % inférieure.

Où le N2 sera-t-il utilisé ? Il trouvera probablement sa place dans toutes sortes de puces, qu’il s’agisse de System on Chip (SoC) mobiles, de cartes graphiques avancées ou de processeurs tout aussi avancés. TSMC a mentionné que l’une des caractéristiques du processus 2 nm est « l’intégration des chiplets ». Cela implique que de nombreux fabricants pourraient utiliser le N2 pour utiliser des boîtiers multi-chiplets afin de mettre encore plus de puissance dans leurs puces.

Des nœuds de processus plus petits ne sont jamais une mauvaise chose. Le N2, une fois qu’il sera là, offrira de hautes performances à toutes sortes de matériels, y compris les meilleurs CPU et GPU, tout en optimisant la consommation d’énergie et les températures. Cependant, jusqu’à ce que cela se produise, nous devrons attendre. TSMC ne commencera pas la production de masse avant 2025, donc, de manière réaliste, il est peu probable que nous voyions des appareils basés sur le 2 nm entrer sur le marché avant 2026.