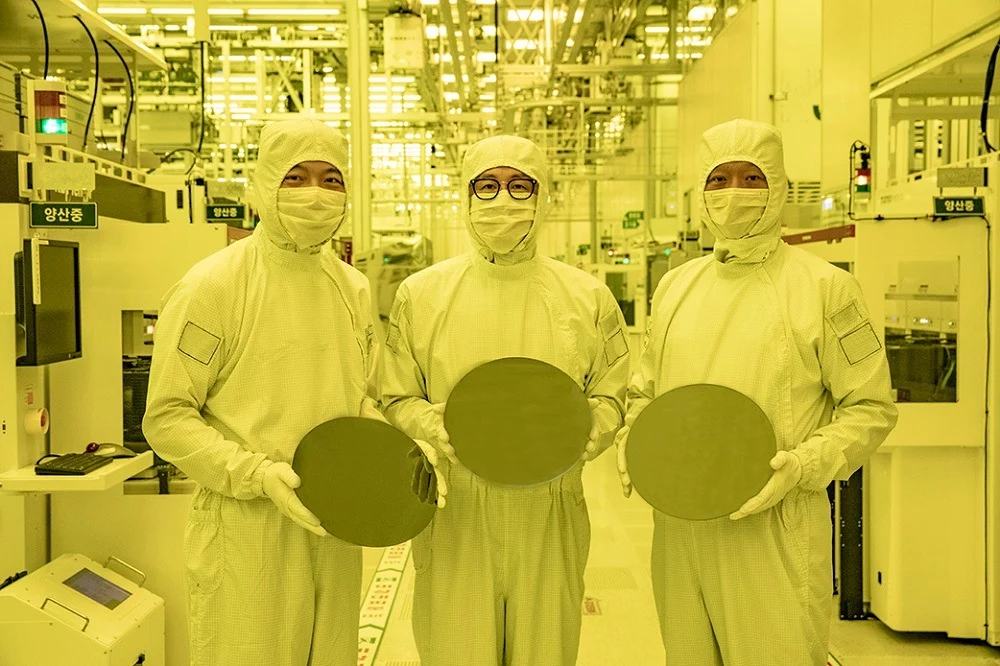

Chez Samsung Electronics, il semble que les problèmes massifs de rendement de puces fonctionnelles dans la nouvelle production en 3 nanomètres aient été à moitié maîtrisés. Samsung vient en effet de lancer officiellement la production de masse de puces en 3 nm.

Samsung est ainsi le premier producteur de semi-conducteurs à pouvoir proposer aux clients la fabrication de puces dans cette taille de structure. Son concurrent, TSMC, veut également lancer sa production en 3 nanomètres cette année, mais le lancement officiel n’a pas encore eu lieu. Ces derniers temps, TSMC n’a pas été confronté à des taux de rebut élevés, de sorte que son rival pourrait facilement compenser son retard en augmentant les quantités livrées et en réduisant les prix.

Pour ses produits en 3 nanomètres, Samsung mise sur la technologie Gate All All Around (GAA). Celle-ci doit offrir différents avantages par rapport à la technique FinFET utilisée jusqu’à présent. Samsung affirme que le nouveau procédé de fabrication est 45 % plus économe en énergie que son précédent procédé de 5 nm, qu’il offre des performances supérieures de 23 % et une surface réduite de 16 %. À l’avenir, Samsung espère que son processus de 3 nm de seconde génération pourra réduire la consommation d’énergie et la taille respectivement de 50 % et 35 %, et augmenter les performances de 30 %.

Il s’agit toutefois de valeurs idéales qui ne sont pas encore atteintes dans la première génération de la nouvelle technique de fabrication — mais les améliorations réalisées jusqu’à présent sont tout de même significatives.

Quoi qu’il en soit, cette annonce est une étape clé dans les efforts de Samsung pour concurrencer TSMC, qui domine le marché de la production de puces à façon et qui est le fabricant des puces d’Apple pour ses iPhone, iPad, MacBook et Mac.

TSMC est dans les starting-blocks

Depuis le troisième trimestre de l’année dernière, le plus grand fabricant mondial de puces mémoires a travaillé avec plusieurs partenaires pour mettre en place les nouvelles lignes de production. L’entreprise technologique allemande Siemens et le concepteur de silicium américain Synopsys y ont notamment participé. La nouvelle technologie de processus sera lancée dans le complexe de Pyeongtaek. Il s’agit de la plus grande usine de semi-conducteurs au monde, située à 70 kilomètres au sud de la capitale sud-coréenne Séoul.

TSMC suivra les Sud-Coréens dans la deuxième moitié de l’année en se lançant dans la production de 3 nanomètres. Entre-temps, les deux leaders du marché travaillent déjà au développement de la technologie en 2 nanomètres. Celle-ci devrait pouvoir être produite en masse à partir de 2025.