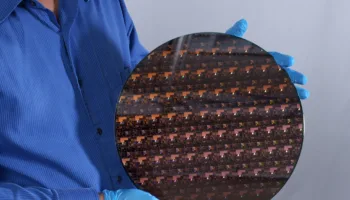

Le terme « rendement » possède de multiples significations selon les domaines. Dans le contexte des fonderies de semi-conducteurs, il désigne le pourcentage de puces utilisables issues d’une tranche de silicium qui réussissent les contrôles de qualité. Un faible rendement peut entraîner une hausse des coûts de production des puces, nécessitant un plus grand nombre de tranches pour atteindre les objectifs de fabrication. Cela réduit les marges bénéficiaires et peut provoquer des pénuries d’approvisionnement.

Leader mondial des fonderies de semi-conducteurs, TSMC, prévoit de démarrer la production de masse de puces en 2 nm dès l’année prochaine. Les tests actuels, réalisés dans l’usine de Zhuke Baoshan située dans le comté de Hsinchu à Taïwan, affichent un rendement de 60 % ou plus. Bien que ce chiffre reste inférieur à la barre des 70 % généralement requise pour la production de masse, il laisse entrevoir une optimisation possible d’ici 2024.

Apple devrait quant à lui continuer d’utiliser le nœud 3 nm de troisième génération (N3P) de TSMC pour ses processeurs A19 et A19 Pro, destinés à équiper la gamme iPhone 17.

Cependant, les premières puces en 2 nm pourraient apparaître sur un iPad Pro de nouvelle génération prévu fin 2025, suivies des iPhone 19 en 2026.

Pourquoi les nœuds de processus sont-ils cruciaux ?

Dans l’univers des semi-conducteurs, la réduction des nœuds de processus (par exemple de 3 nm à 2 nm) signifie des transistors plus petits. Cela permet :

- Une augmentation de la densité de transistors : Plus de transistors dans une même surface de puce, augmentant la puissance et l’efficacité énergétique.

- Des gains en performance et en efficacité : Les puces gravées sur des nœuds plus fins consomment généralement moins d’énergie tout en offrant de meilleures performances.

Avec son nœud de 2 nm, TSMC introduit une nouvelle technologie de transistor appelée Gate-All-Around (GAA). Contrairement à la précédente génération (FinFET), où le canal était couvert sur trois côtés, les transistors GAA entourent le canal sur ses quatre côtés grâce à des nanosheets horizontaux positionnés verticalement. Cela réduit les fuites électriques et améliore les courants de conduction, offrant ainsi des performances accrues.

TSMC face à Samsung : un duel technologique

Si TSMC progresse vers un rendement acceptable pour le 2 nm, son principal concurrent, Samsung Foundry, rencontre des difficultés importantes. Les rumeurs évoquent des rendements compris entre 10 % et 20 % pour ses tests en 2 nm. Ces faibles chiffres alimentent des spéculations sur l’éventuelle annulation du Exynos 2600, une puce censée être produite avec ce nœud.

Les problèmes de rendement ne sont pas nouveaux pour Samsung. En 2022, ses faibles résultats pour la production du Snapdragon 8 Gen 1 avaient conduit Qualcomm à transférer sa production à TSMC. Ce transfert a donné naissance au Snapdragon 8+ Gen 1, marquant un tournant dans la collaboration entre Qualcomm et TSMC.

Le futur des semi-conducteurs

TSMC est bien positionné pour dominer le marché des puces en 2 nm, en exploitant des avancées technologiques clés et en optimisant ses rendements. Cette transition vers des nœuds plus fins représente une étape cruciale pour les fabricants de semi-conducteurs, où chaque gain de performance peut transformer les industries dépendantes des technologies mobiles, des serveurs et de l’IA.

Pour les consommateurs, ces innovations se traduiront par des appareils plus rapides, plus efficaces et plus intelligents, posant les bases des futures générations de smartphones et de produits connectés.